短絡耐量試験の概要および特徴

パワー半導体の信頼性試験における短絡状態とは

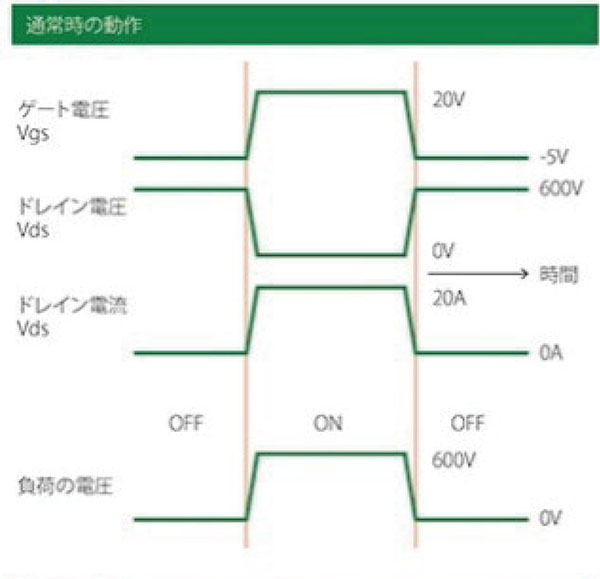

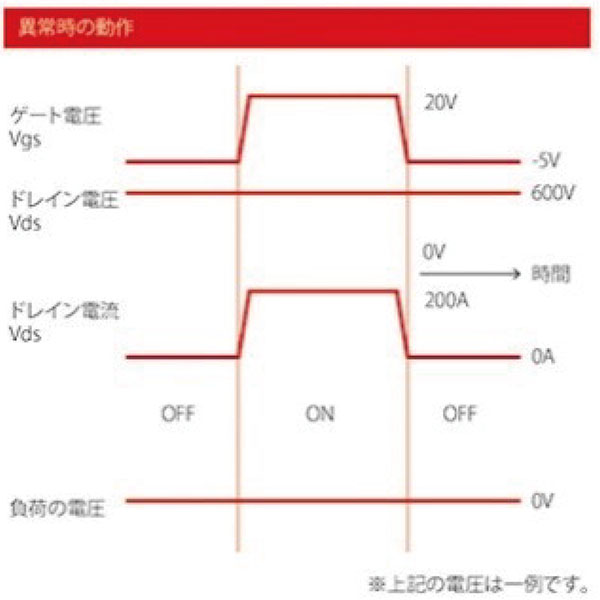

通常、パワー半導体デバイスは、高速のスイッチとして動作します。

スイッチとして動作しているときは、オフ(電圧:大、電流:微小)とオン(電圧:小、電流:大)の二つの状態を繰り返します。

このような通常動作の場合、パワー半導体でのロス(電圧×電流)、すなわち発熱は比較的小さくなり、負荷に大きな電力が与えられます。

ところが、なんらかの異常が発生し、負荷が短絡(ショート)状態になると、負荷の電圧がゼロになるため、パワー半導体に大きな電圧が印加された状態で、大電流が流れてしまい、その結果大電力が半導体チップに加わり、チップ温度Tjが急激に上昇します。

そして、ごく短時間のうちにデバイスが破壊してしいます。

短絡耐量試験の設計

短絡耐量試験では負荷短絡の状態でデバイスをオン状態にし、破壊に至るまでの時間Tscを測定します。

破壊の過程で、パッケージが大音響で破裂する場合もあり、危険を伴います。

パワー半導体を使った機器を設計する場合に負荷短絡状態になってもデバイスが破壊することが無い様に、保護回路を設ける必要があり、Tscより十分短い時間で、保護回路が動作するように設計します。

特に、SiCMOSFETはチップサイズが小さくなる傾向があり、SiMOSFETに比べてTscが小さくなる傾向があります。

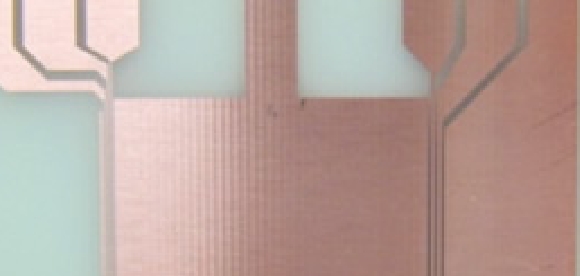

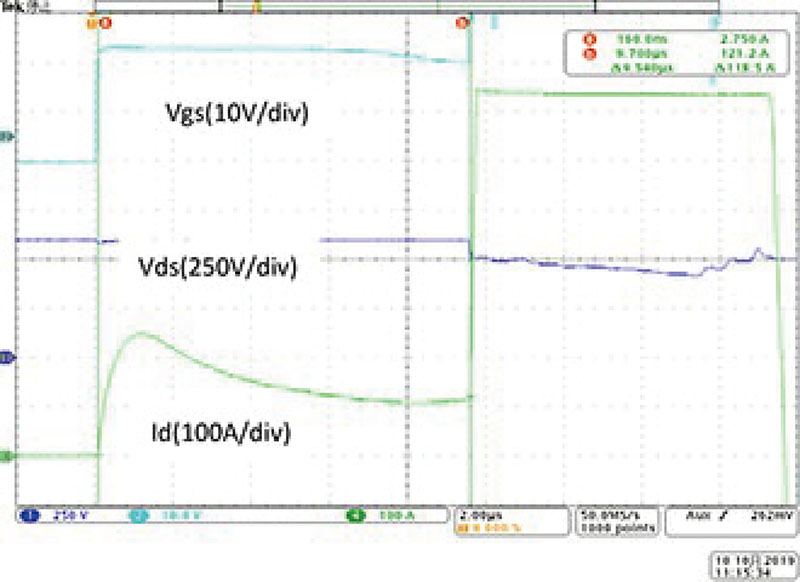

下の図は、実際の試験例です。

Vds=600V、Vgs=18Vの条件で、Tsc=9.5μsecという結果です。

短絡耐量試験における測定回路

DUTはSi、SiCパワーMOSFETです。

1kV1000μFの大容量のコンデンサをDUTに低インピーダンスで接続します。最大800Vまで出力できる電源からこのコンデンサに充電し、ゲートパルスを印加します。

ゲートドライバー回路はDUTの破壊に伴って破壊しますので、毎回交換します。

短絡耐量試験の全景

デバイスは破裂してパッケージが飛び散る場合があるため、厚さ10mmのアクリルケース内で試験を行います。

また、大電流を供給する大容量のコンデンサとDUTは低インピーダンスで接続する必要があるため、特殊構造により、これを実現しています。